### Vedic Optimized ALU with a new Approach Urdhva Triyambakam Multiplier

Nidhi Rajput

Research Scholar Takhshshila Institute of Engineering and technology, Jabalpur (M.P.) [INDIA] Email: nidhirajput1991@gmail.com

#### ABSTRACT

For Fast Operations multiplication is very important in Arithmetic Unit. Available Vedic hardware multiplication has certain limitations, if area is in concern. To reduce these limitations a different approach has been proposed to design the Vedic multiplier with new proposed addition structure. To meet major concern i.e. 'Speed', proposed work need a high speed ALU. The speed of ALU generally depends upon the speed of its multiplication unit used. Proposed multiplication techniques Vedic and tree addition structure gives a very fast and area optimized multiplication method. The proposed model gives ALU algorithm which is efficient in both area and speed.

**Keywords:**—EDA, VLSI, Vedic, Wallace, DSP- Digital Signal Processing, ISE, HDL-Hardware Descriptive Language, MAC, CSA, ISE- Integrated Synthesis Environment.

### I. INTRODUCTION

Vedic Mathematics is the ancient way of mathematics which has a various technique of calculations based on around 16 Sutras<sup>[8]</sup>. There is various multiplication techniques exist now a days at structural and algorithmic level. It has been proved that vedic multiplications the fastest multiplication approach among all

### **Rakesh Patel**

Assistant Professor. Department of Electronics and Communication, Takhshshila Institute of Engineering and technology, Jabalpur, (M.P.) [INDIA] Email:rakeshpatel04@gmail.com

other multiplication techniques<sup>[1]</sup> but there are some different multiplication techniques which are better than vedic multiplication when chip area is in concern<sup>[2][4].</sup>

By improving the ALU unit one can develop efficient Digital Signal Processor, for which proposed Arithmetic unit appears very useful. One of the major aspects of Vedic mathematics is to execute the tedious calculations in simple manner, even orally computable without use of pen and paper<sup>[3][5]</sup>. Anyone can do these operations for small numbers and hence Vedic mathematics give methods to solve operations with higher value numbers in a very easy and fast manner. Vedic mathematics has more than one approach for every basic arithmetic computation like multiplication and division. For each operation there is minimum one defined method provided along with few generic methods which are dedicated towards particular cases simplifying the calculations further. Paper <sup>[6]</sup> and <sup>[7]</sup> described the Vedic mathematics from staring and discuss all methods and computation. Vedic mathematics provides algorithms to simple the mathematics and that makes it best solution for the problems with speed. Proposed paper work has used the Urdhva Triyambakam sutra for multiplication. Designing is done with the tree addition structure instead of the Conventional Adder, which is required during the Partial Product generation is known tree method, converts the

9

Vedic Optimized ALU with a new Approach Urdhva Triyambakam Multiplier Author (s): Nidhi Rajput, Rakesh Patel | Takshshila, Jabalpur

multi-operand addition into the easy two operand Addition and it takes less time.

### **II. PROPOSED ARITHMETIC UNIT**

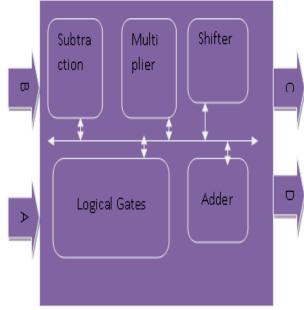

Proposed 16x16 bit Arithmetic Unit is shown in the figure 1.

Figure 1. Arithmetic Logic Unit Module

A and B are the two 16 bit inputs for proposed Arithmetic Unit and internal part of the design includes Subtractor, Adder, Multiplier, shifter and logical Gates. Product and Accumulated product are of 32 bit output while subtraction and addition are of 16 bit output. Proposed work never focus on the designing of the adder or subtractor circuits, as known these are not consider as modules which requires large amount of area and power in ALU. But after lots of study it is been found that multiplier is the module which consumes lots of area, time and power, so Vedic multiplication is been developed with new addition tree structure to meet timing constraints.

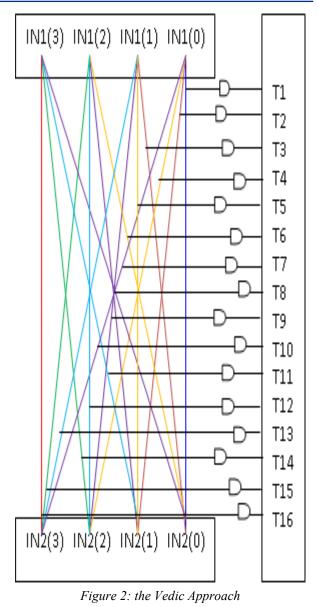

For proposed approach of multiplication IN1 and IN2 are the two inputs. Now as per Vedic approach it requires 16 logical AND operations with specific crosswise values of given number binary digits.

After logical AND cross wise operation obtained values are t1, t2, t3......t16. To add these values addition structure as shown in figure 3 below.

| -we n | eed t | o add |     |     |    |    |    |  |

|-------|-------|-------|-----|-----|----|----|----|--|

| '0'   | t16   | t14   | t11 | t7  | t4 | t2 | t1 |  |

|       |       | t15   | t12 | t8  | t5 | t3 |    |  |

|       |       |       | t13 | t9  | t6 |    |    |  |

|       |       |       |     | t10 |    |    |    |  |

Figure 3: Vedic Intermediate data

10

|     |        |            | carry sav  |            |            |       |    |

|-----|--------|------------|------------|------------|------------|-------|----|

| 0'  | t16    | t14        | t11        | t7         | t4         | t2    | t1 |

|     |        | t15        | t12        | t8         | t5         | t3    |    |

|     |        |            | t13        |            | t6         |       |    |

|     | t16    |            | <b>s</b> 3 |            | s1         | t2    | t1 |

|     |        | t15        | c2         | c1         |            | t3    |    |

|     |        | c3         |            | t10        |            |       |    |

|     | t16    | <b>s</b> 5 | <b>s</b> 3 | s4         | s1         | t2    | t1 |

|     | c5     |            | c2         |            |            | t3    |    |

|     |        |            | c4         |            |            |       |    |

|     | t16    |            | 36         |            |            | t2    | t1 |

|     | c5     | c6         |            |            |            | t3    |    |

| c12 | s12    | s11        | s10        | <b>8</b> 9 | <b>5</b> 8 | s7    | t1 |

| j   | Figure | 4: the p   | proposed   | d additi   | ion stru   | cture |    |

*Vedic Optimized ALU with a new Approach Urdhva Triyambakam Multiplier Author (s): Nidhi Rajput, Rakesh Patel | Takshshila, Jabalpur*

Figure 4 shows the way of performing addition, in this way one can have minimum hardware required as compare with Wallace addition or carry save addition. Proposed addition method requires only 8 full adder and 4 half adder while Wallace addition in this

scenario requires total 7 full adders and 8 half adders and carry save adder requires 8 full adders and 7 half adders. It shows that proposed method needs minimum area.

### **III. RESULTS**

### Table1: Results Observed for 4x4 ProposedVedic Tree Multiplier

| No of Slices          | 452      |

|-----------------------|----------|

| No of 4 input LUT     | 803      |

| No of bounded<br>IOBs | 68       |

| Logical Delay         | 9.007 ns |

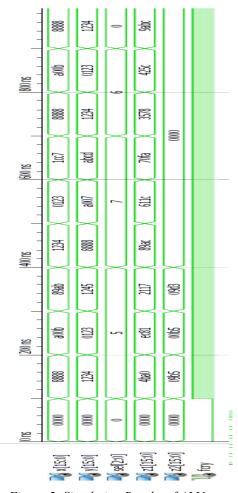

Proposed work shows new design for 4 bit Vedic multiplier with the help of Tree adder. Table 1, 2 and 3 given below shows the results for the design of 4x4, 8x8, and 16x16 which has also been implement with new proposed 4x4 Vedic tree multiplier. Figure 5 below shows the simulation results of the ALU module design and it shows the results of subtraction, multiplication and addition.

Figure 5: Simulation Results of ALU

Table2: Results Observed for 8x8 ProposedVedic Tree Multiplier

| No of Slices          | 18       |

|-----------------------|----------|

| No of 4 input LUT     | 31       |

| No of bounded<br>IOBs | 16       |

| Logical Delay         | 4.891 ns |

# Table 3: Results Observed for 16x16Proposed Vedic Tree ALU

| No of Slices          | 90       |

|-----------------------|----------|

| No of 4 input LUT     | 158      |

| No of bounded<br>IOBs | 32       |

| Logical Delay         | 6.468 ns |

### Table 4: Comparative Results of ProposedVedic 4x4 with Other Available

|                                    | Logical<br>Delay | Slice |

|------------------------------------|------------------|-------|

| Proposed Vedic<br>4 bit multiplier | 4.891 ns         | 18    |

| Ref4                               | 6.216 ns         | 27    |

| Ref 5                              | -                | 25    |

| Base 3                             | 10.95 ns         | 20    |

## Table 5: Comparative results of proposedVedic 8x8 with other available

|                                       | Logical Delay | Slice |

|---------------------------------------|---------------|-------|

| Proposed<br>Vedic 8 bit<br>multiplier | 6.468 ns      | 90    |

| Ref3                                  | 36.563 ns     | -     |

| Ref2                                  | 15.685 ns     | -     |

| Ref1                                  | 15.484 ns     | -     |

| Ref5                                  | 15.518 ns     | -     |

# Table 6: Comparative Results of ProposedVedic ALU with others

| Design                         | Sub design s<br>(If any) | Logical<br>Delay | Slice |

|--------------------------------|--------------------------|------------------|-------|

| Proposed<br>Vedic 4 bit<br>ALU |                          | 5.623 ns         | 18    |

| Base 3 (4x4<br>ALU)            |                          | 10.95 ns         | 20    |

|                                |                          |                  |       |

| Design                         | Sub design s<br>(If any) | Logical<br>Delay | Slice |

| Proposed<br>Vedic 8 bit<br>ALU |                          | 6.655 ns         | 90    |

| Base 1 (8x8 bit<br>multiplier) | Kartsuba                 | 31.029 ns        | -     |

|                                | Vedic kart-<br>suba      | 18.695 ns        | -     |

|                                | Optimized<br>Vedic       | 15.418 ns        | -     |

| Base 2 (8x8<br>ALU)            |                          | 48.80 ns         | -     |

| Base 3(8x8<br>ALU)             |                          | 15.52 ns         | 92    |

The results have been generated after RTL entry in Xilinx EDA tool. Verification is done on Xilinx ISE and all results have been verified correctly. Above proposed results are batter in terms of area (means less number of Slice) and speed (means less logical delay) in 4 bit ALU and multiplication as compare to base paper number 3.

Above as can observe that proposed results are better in aspect of speed (means logical delay) in 8 bit as compare to base papers 1, 2 and 3.

Proposed work has designed 4 bit Vedic multiplier (original research work) and uses it to design with 16 bit ALU.

*Vedic Optimized ALU with a new Approach Urdhva Triyambakam Multiplier Author (s): Nidhi Rajput, Rakesh Patel | Takshshila, Jabalpur*

Figure 6 shows power of proposed work which is designed with the help of X power analyzer for final validation of design on FPGA.

| 🖥 🖬 🕫 -         | a - A          | 80 48            | 1           |                                                                |                    |        |         |              |   |

|-----------------|----------------|------------------|-------------|----------------------------------------------------------------|--------------------|--------|---------|--------------|---|

|                 |                |                  | 1           |                                                                |                    | *      |         |              |   |

|                 | Voltage (V)    | Current (mA      | Power (mW 🔺 | Power summary:                                                 |                    | I (nA) | P (mW)  |              |   |

| ccint           | 18             |                  |             |                                                                |                    |        |         |              |   |

| Dynamic         |                | 0.00             | 0.00        | Total estimated power cons                                     | amption:           |        | 25      |              |   |

| Quiescent       |                | 10.00            | 18.00       |                                                                |                    |        |         |              |   |

| cco33           | 33             |                  |             |                                                                | nt 1.80V:          | 10     | 18      |              |   |

| Dynamic         |                | 0.00             | 0.00        | Vcco                                                           | 33 3.30V:          | 2      | 7       |              |   |

| luiescent       |                | 2.00             | 6.60        |                                                                |                    |        |         |              |   |

| stal Powe       |                |                  | 24.60       |                                                                | Inputs:            | 0      | 0       |              |   |

| artup Curre     |                | 500.00           |             |                                                                | Logic:             | 0      | 0       |              |   |

|                 | ity (mA Hours) |                  | 0.00        |                                                                | Vcco33             | 0      | 0       |              |   |

| attery Life (Ho | 0015)          |                  | 0.00 *      |                                                                | vccoss<br>Signals: | 0      | 0       |              |   |

| unmay Ro        | wy Subtrids    | Current Subbalis | Trenal      |                                                                | arduarg:           | V      | U.      |              |   |

|                 |                |                  |             | Quiescent Vccin                                                | 1 8011             | 10     | 18      |              |   |

|                 |                |                  | x           | Quiescent Vccc3                                                |                    | 2      | 7       |              |   |

| Data Viel       |                |                  |             | Aurosonie 10000                                                |                    |        | ,       |              |   |

| 🗄 🗎 Types       |                |                  |             | Thermal summary:                                               |                    |        |         |              |   |

| Report V        |                |                  |             |                                                                |                    |        |         |              |   |

|                 | Report (HTM    | L)               |             | Estimated junction temp                                        | erature:           |        | 26C     |              |   |

| Power           | r Report       |                  |             | Ambient                                                        | temp: 25C          |        |         |              |   |

|                 |                |                  |             | Case                                                           | temp: 260          |        |         |              |   |

|                 |                |                  |             | Theta J-A r                                                    | ange: 35 -         | 36C/W  |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

|                 | dealers &      |                  | the state   | in for the last of the last                                    |                    |        | 10.01   |              | _ |

|                 |                |                  |             | vice from file '2s50e.nph' in<br>, device xc2s50e, package pg2 |                    |        | 1nx921. |              | í |

| INFO:           | (6010 18       | an NCD, Y        | WESTON 2.1  | A gearce xcrapael beckede bda                                  | .vo, speed -       |        |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

|                 |                |                  |             | d using PRELIMINARY data.                                      |                    |        |         |              |   |

|                 |                |                  |             | a asing recontinent data.                                      |                    |        |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

|                 |                |                  |             |                                                                |                    |        |         |              |   |

| Help, press     |                |                  |             |                                                                |                    |        | NUM     | 2s50epq208-7 |   |

Figure 6: the power report of proposed work

#### **IV. CONCLUSION**

Proposed work is a design of 16x16 bit Multiplier which produces better results with respect to the all available Vedic multiplier or another Multiplier. Proposed design makes optimized multiplier and very useful for designing the delay and area optimized ALU, which enhance the Microprocessor, because its performance is dependent on the efficiency of ALU. Proposed design can also be used for make efficient ALU unit of DSP, and hence optimized designs can also be used to design FFT, FIR, IIR, and DFT and their performance is directly dependent on the speed of ALU unit.

### **REFERENCES:**

[1] Nidhi Rajput, Rakesh Patel 'An approach of Vedic Multiplication Technique for optimizing logic delay in MAC Unit', International Journal of Modern Engineering and Management Research, Volume 2, Issue 1,pp 65-69, March 2014

- [2] Vaijyanath Kunchigi, Lingana gouda Kulkarni, Subhash Kulkarni, 'High Speed and Area Efficient Vedic Multiplier', IEEE 2012.

- [3] Pavan Kumar U.C.S1, Saiprasad Goud A2 A.Radhika, 'FPGA Implementation of high speed 8-bit Vedic multiplier using barrel shifter', 2013 IEEE.

- [4] Rakshith Saligram, Rakshith T. R, 'Optimized Reversible Vedic Multipliers for High Speed Low Power Operations', Proceedings of 2013 IEEE Conference on Information and Communication Technologies (ICT 2013).

- [5] Anvesh Kumar, Ashish Raman, 'Low Power ALU Design by Ancient Mathematics', 2010 IEEE.

- [6] M. Ramalatha, Senior Member, IEEE, K. Deena Dayalan, Member, IEEE, P. Dharani, Member, IEEE, S. Deborah Priya, Member, IEEE, 'High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques', July 15-17, 2009 Zouk Mosbeh, Lebanon, 2009 IEEE.

- [7] Vedic Mathematics, Jagadguru Swami Sri Bharati Krsna Tirthatji Maharaja, Motilal Banarsidass Publication, 1992.

- [8] Vedic Maths facts and myths, S.G. Dani, Vol 4/6, January 2001, pp. 20-21, One India One People.

- [9] www.xilinx.com

#### \* \* \* \* \*