## A Novel Approach for Arithmetic Execution Unit for High Speed Application

Raunak Mathurker Research Scholar, (M.Tech.) Takshshila Institute of Engineering and Technology Jabalpur (M.P.), [INDIA] Email:

#### ABSTRACT

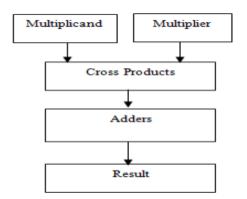

This paper presents Multiply and Accumulate (MAC) unit design using Vedic Multiplier, which is based on Urdhva Tiryagbhyam Sutra. The paper emphasizes an efficient 32bit MAC architecture along with 8-bit and 16bit versions and results are presented in comparison with conventional architectures. The efficiency in terms of area and speed of proposed MAC unit architecture is observed through reduced area, low critical delay and low hardware complexity. The proposed MAC unit reduces the area by reducing the number of multiplication and addition in the multiplier unit. Increase in the speed of operation is achieved by the hierarchical nature of the Vedic multiplier unit. The performance evolution results in terms of speed and device utilization are compared to earlier MAC architecture.

*Keywords:*—*Vedic Multiplier AEU, FPGA, Xilinx-ISE 14.1*.

#### **I. INTRODUCTION**

The general MAC architecture consists of a conventional multiplier, adder and an accumulator. Where the output is added to the previous MAC output result by an accumulate adder. The Multiply-Accumulate (MAC) unit is extensively used in microprocessors and digital signal processors for data-intensive

#### Shivam Solanki Assistant Professor ment of Computer Science & Engined ila Institute of Engineering and Tech

Department of Computer Science & Engineering Takshshila Institute of Engineering and Technology Jabalpur (M.P.), [INDIA] Email:shivamsolanki@takshshila.org

applications, such as filtering, convolution, and inner products. Most digital signal processing methods use nonlinear functions such as discrete cosine transform (DCT) or discrete wavelet transform (DWT) or FFT/IFFT computations that can be efficiently accelerated by dedicated MAC units. Because they are basically accomplished by repetitive application of multiplication and addition, the speed of the multiplication and addition determines the execution speed and performance of the entire computation. As the multiplier exhibits inherently long delay among the basic operational blocks in digital system, the multiplier determines the critical path. In order to improve the speed of the MAC unit, there are two major bottlenecks. The first is the partial products reduction network that is used in the multiplication block and the second is the accumulator. Both of these stages require addition of large operands that involve long paths for carry propagation. The main key to the proposed architecture is using the Vedic multiplier to design the MAC unit and compare the performance with the conventional MAC units in terms of area, speed and number of resources.

In computing, especially digital signal processing, most common operation is which get performed is arithmetic operation.

A Novel Approach for Arithmetic Execution Unit for High Speed Application Author(s): Raunak Mathurker, Shivam Solanki, TIET, Jabalpur

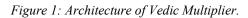

The AEU unit shown in the block diagram is able to perform arithmetic operations such as Addition, Subtraction, Multiplication, Squaring and comparison operations. Furthermore arithmetic operations are also very important and dominant for digital filters.

#### **II. Proposed AEU Unit**

#### Proposed Multiplication Unit design:-

Multiplication Accumulation is an important part of real-time digital signal processing (DSP) with applications ranging from digital filtering to image processing. Multiply and accumulate is a very common basic-level operation seen in many DSP designs/algorithms. Two numbers are multiplied together, and added into an accumulator register. As shown in Fig.4, the basic MAC unit consists of multiplier, adder and accumulator. In general MAC unit uses the conventional multiplier unit, which consists of multiplication of multiplier and multiplicand based on adding the generated partial products and to compute the final multiplication. This results to adding the partial products. The key to the proposed MAC unit is to enhance the performance of MAC using Vedic Multiplier and to compare the Vedic, Booth and conventional multiplier in terms of computation required to generate the partial products and add the generated partial products

to get the final result of the multiplication For 2 bit level we have proposed to use conventional Vedic multiplier, whose digital hardware is shown below:-

Figure 2 : Proposed Four Bit Vedic Multiplier Using Divide And Conquer Approach

In the above diagram the oval shape multiplier and multiplicand represents respectively. And the line between these oval shapes represents that multiplication operation being occurred. It can be seen from above given diagram that to multiply four-bit numbers say b [3:0] and a [3:0], four submultiplication operations need to be performed, using the two bit Vedic multiplier. Means to perform the four-bit multiplication, the two-bit multiplier has been instantiated four times. Then the addition tree structure has been used to add these partially generated product outputs of two-bit multiplier. As shown in the following:-

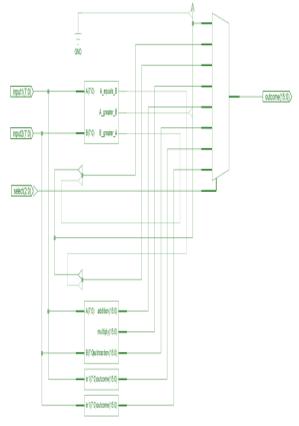

Figure 3: Top View of AEU

A Novel Approach for Arithmetic Execution Unit for High Speed Application Author(s): Raunak Mathurker, Shivam Solanki, TIET, Jabalpur

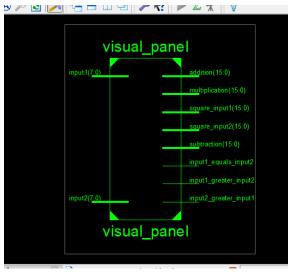

Figure 4: RTL view of AEU

#### **III. SIMULATION AND SYNTHESIS RESULT**

1. Platform being used: - For this design the target FPGA, which has been used belongs to Spartan-2 (family), XC2S200 (device), PQ208 (package) with speed grade of -6. Xilinx synthesis tool (XST) of Xilinx ISE-14.1 has been used for synthesis purpose. For the behavioural simulation purpose ISE simulator has been used.

| Property Name                  | Value                        | * |

|--------------------------------|------------------------------|---|

| Product Category               | General Purpose 🔹            |   |

| Family                         | Spartan2                     |   |

| Device                         | XC2S200                      |   |

| Package                        | PQ208                        |   |

| Speed                          | -6 💌                         |   |

|                                |                              | E |

| Top-Level Source Type          | HDL                          |   |

| Synthesis Tool                 | XST (VHDL/Verilog)           |   |

| Simulator                      | ISE Simulator (VHDL/Verilog) |   |

| Preferred Language             | Verilog 🔹                    |   |

|                                |                              |   |

| Enable Enhanced Design Summary |                              |   |

| Enable Message Filtering       |                              | Ŧ |

Figure 5: Target FPGA for our module

Figure 6. 8-Bit Vedic Multiplier RTL Schematic

Figure 7 : Proposed 8 Bit Single Visual Panel RTL Schematic

#### 2. Device Utilization Summary:-

| Device Utilization Summary                     |       |           |             |         |  |

|------------------------------------------------|-------|-----------|-------------|---------|--|

| Logic Utilization                              | Used  | Available | Utilization | Note(s) |  |

| Number of 4 input LUTs                         | 376   | 4,704     | 7%          |         |  |

| Logic Distribution                             |       |           |             |         |  |

| Number of occupied Slices                      | 211   | 2,352     | 8%          |         |  |

| Number of Slices containing only related logic | 211   | 211       | 100%        |         |  |

| Number of Slices containing unrelated logic    | 0     | 211       | 0%          |         |  |

| Total Number of 4 input LUTs                   | 411   | 4,704     | 8%          |         |  |

| Number used as logic                           | 376   |           |             |         |  |

| Number used as a route-thru                    | 35    |           |             |         |  |

| Number of bonded <u>IOBs</u>                   | 35    | 140       | 25%         |         |  |

| Total equivalent gate count for design         | 3,345 |           |             |         |  |

| Additional JTAG gate count for IOBs            | 1,680 |           |             |         |  |

Figure 8: Device Utilization Summary of Proposed 8-Bit Arithmetic Execution Unit

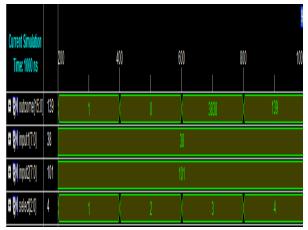

### Simulation Results:-

Proposed 8-bit Arithmetic Execution Unit simulation waveform, where inputs and output are in decimal format: -

Figure 9: Proposed 8-Bit AEU Unit Simulation Waveform

#### **IV. COMPARATIVE RESULTS**

Proposed Arithmetic Execution Unit (AEU)'s solely depends speed upon effectiveness and efficiency of proposed Vedic multiplier. That's why to showcase efficiency and effectiveness of proposed Vedic multiplier that has been implemented and compared with commercially other popular available multiplication structures lie on different multiplication algorithms on the same platform of target FPGA, which has been used to implement these popular multiplier structures.

Proposed module has been compared against different modules with same target FPGA on which previous has been implemented and then showcased comparison on the basis of availability of results. Comparison tables are shown below:-

# Table 1: Comparison Modules with SameTarget FPGA

| Parameters             | Vishal Galphat, Nitin<br>Lonbale [1] | Result Obtained |

|------------------------|--------------------------------------|-----------------|

| No. of slice LUTs      | 17                                   | 14              |

| No. of bonded IOBs     | 18                                   | 16              |

| Propagation Delay (ns) | 7.881                                | 7.858           |

#### **V. CONCLUSION**

In this research work a thorough analysis and study work has been done on Vedic multipliers and we have found that Vedic with CSA provides much better outcome than commercially available multipliers likewise Booth, Wallace, Modified Booth Wallace multipliers etc. So we have used this multiplier to perform all multiplication operations being used in various operations of Arithmetic Execution Unit those are square and multiplication unit. After synthesis and simulation work for proper validations has been performed on this AEU to have reliability on our proposed designed module.

#### **VI. APPLICATION**

Arithmetic Execution Unit performed operations are very important and dominant for digital filters. Therefore, by the use of speed optimized AEU high-speed filtering can be achieved.

A Novel Approach for Arithmetic Execution Unit for High Speed Application Author(s): Raunak Mathurker, Shivam Solanki, TIET, Jabalpur

AEU is also useful to optimize other processing typical for DSP applications.

#### **REFERENCES:**

- [1] Shivakumar M V, Mrs. Anitha Kumari, "A Novel approach towards performance analysis Of Vedic multiplier using FPGA's", International Journal of Electronics, Electrical and Computational System IJEECS ISSN 2348-117X Volume 3, Issue 4 June 2014.

- [2] Sudeep. M.C, Sharath Bimba. M, Mahendra Vucha," Design and FPGA Implementation of High Speed Vedic Multiplier", International Journal of Computer Applications (0975 – 8887) Volume 90 – No 16, March 2014.

- [3] Pushpalata Verma and K.K. Mehta "Implementation of an efficient Multiplier based on Vedic Mathematics using EDA tool.", International Journal of Engineering and Advanced Technology (IJEAT) ISSN: 2249 – 8958, Volume-1, Issue-5, June 2012.

- [4] G.Ganesh Kumar, V.Charishma, "Design of High Speed Vedic Multiplier Using Vedic Mathematics Techniques", International Journal of Scientific and Research Publications, Volume 2, Issue 3, March 2012 1 ISSN 2250-3153.

- [5] Gaurav Sharma, Arjun Singh Chauhan, Himanshu Joshi, Satish Kumar Alaria, "Delay Comparison of 4 by 4 Vedic Multiplier based on Different Adder Architectures using VHDL", International Journal of IT, Engineering and Applied Sciences Research (IJIEASR) ISSN: 2319-4413 Volume 2, No. 6, June 2013.

- [6] Mohammed Hasmat Ali, Anil Kumar Sahani, "Study, Implementation and Comparison of Different Multipliers based on Array, KCM and Vedic Mathematics Using EDA Tools", International Journal of Scientific and Research Publications, Volume 3, Issue 6, June 2013 ISSN 2250-3153.

- [7] Krishnaveni D., Umarani T.G., "VLSI Implementation of Vedic Multiplier with Reduced Delay", International Journal of Advanced Technology & Engineering Research (IJATER) National Conference on Emerging Trends in Technology (NCET-Tech).

- [8] Devika Jaina, Kabiraj Sethi, Rutuparna Panda, "Vedic Mathematics Based Multiply Accumulate Unit", IEEE, 978-0-7695 -4587-5/11, 2011.

- [9] M. Ramalatha, K. Deena Dayalan, P. Dharani, S. Deborah Priya, "High Speed Energy Efficient ALU Design using Vedic Multiplication Techniques", IEEE, 978-1-4244-3834 -1/09, 2009.

- [10] Ramesh Pushpangadan, Vineeth Sukumaran, Rino innocent, Dinesh sasikumar, Vaisak Sundar, "High Speed Vedic Multiplier for Digital Signal Processors", IETE Journal of Research, Volume 55, Issue 6, Nov-Dec 2009.

- [11] S.S. Kerur, Prakash Narchi, Jayashree C N, Harish M. Kittur, Girish V A, "Implementation of Vedic Multiplier for Digital Signal Processing", proceedings published by International Journal of Computer Applications, presented in International conference on VLSI, Communication and Instrumentation

A Novel Approach for Arithmetic Execution Unit for High Speed Application Author(s): Raunak Mathurker, Shivam Solanki, TIET, Jabalpur

(ICVCI) 2011.

- [12] V.K. Karthik, Y. Govardhan, V. Karunakara Reddy, K. Praveena, "Design of Multiply and Accumulate Unit using Vedic Multiplication Techniques", International Journal of Scientific & Engineering Research, Volume 4, Issue 6, June-2013 756 ISSN 2229-5518.

- [13] Vaijyanath Kunchigi, Linganagouda Kulkarni, Subhash Kulkarni, "32 Bit MAC unit Design Using Vedic Multiplier", International Journal of Scientific and Research Publications, Volume 3, Issue 2, February 2013 1 ISSN 2250-3153.

- [14] Manoranjan Pradhan, Rutuparna Panda, Sushanta Kumar Sahu, "MAC Implementation using Vedic Multiplication Algorithm", International Journal of Computer Applications (0975 – 8887) Volume 21–No.7, May 2011.

\* \* \* \* \*