# International Journal of Modern Engineering and Research Technology

Website: http://www.ijmert.org

Email: editor.ijmert@gmail.com

ISSN: 2348-8565 (Online)

# **VLSI Implementation of FPGA based 8 bit Barrel Shifter**

#### Sarika Patel

M.E. Research Scholar Takshsila Institute of Engineering & Technology Jabalpur (M.P.), [INDIA] Email: sarika.patel2@gmail.com

#### **ABSTRACT**

Barrel shifter is a digital circuit that can move an information word by a predefined number of bits. Barrel shifters are applicable for digital signal processors. Several types of shifting operations exist depending on the target application, including shift logical, shift arithmetic and rotate. In this work a set of hardware design alternatives for shifters to perform the different types of shifting operations was analyzed, designed and implemented in a Virtex-4- FPGA. arithmetic and logic operations barrel shifters is used to shift a desired number of bits in a desired direction. In this paper an 8-bit & an 16-bit barrel shifter architecture is proposed and implemented using Verilog code.

**Keywords:**— barrel shifter, Multiplexer, rotate left, shifter, right shift, logical right, fpga.

### I. INTRODUCTION

A Barrel Shifter is a logic component that performs shift or rotate operations. Barrel shifters are applicable for digital signal processors. This component design is for natural size (4, 8, 16...) barrel shifters that perform shift right logical, shift left logical, rotate left and rotate right operations depending on the instantiation parameters. The left and right operation is implemented through inversion of the input and output vectors. The

#### Shivam Singh Solanki

Assistant Professor

Department of Electronics & Communication Engg.

Takshsila Institute of Engineering & Technology

Jabalpur (M.P.), [INDIA]

Email: shivamsolanki@takshshila.org

number of multiplexing stages is relative to the width of the input vector.

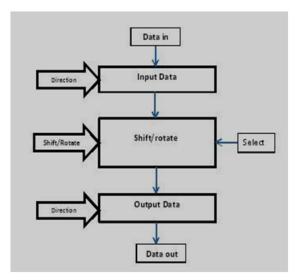

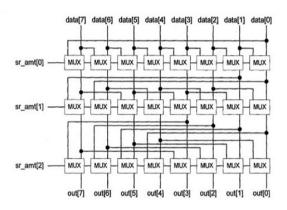

Figure 1. Block Diagram of Barrel Shifter

Shifting and rotating data is required in several applications including arithmetic operations, variable length coding, are bit indexing. Consequently, barrel shifters which are capable of shifting or rotating data in a single cycle. Select lines are used to specify the amount of shift only. A barrel shifter can be designed by using mux trees.

# Architecture

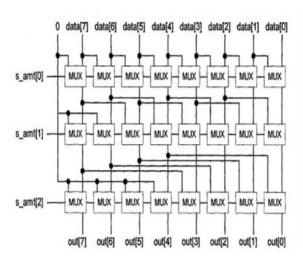

#### 1. Logical right shifter:

A logical right shifter using a fore mentioned approach is shown in the figure 1. The first row corresponds to a shift of one, while the last row

corresponds to a shift of four, As required, zeros fill the high order region. Hence, interconnects route zero into the high order multiplexers. The values x\_amt[x] represents the bit in position x of the shift amount, and as such represents the value  $2^x$ ,

Figure 2. Logical Right Shifter

## 1.1 Operation of right shifter:

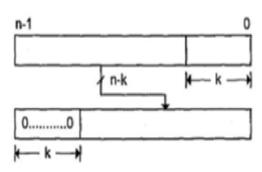

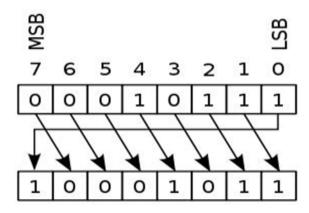

The shift right logical operation is much like a rotate right but without the lower order bits (LSB) being moved to a high order (MSB) position. Instead, the LSB bits are removed. The remaining bits are shifted to the right so as to fill the void created by the loss of the low order bits (LSB). The void created in the MSB region by this shift is filled with zeros.

Figure 3. Right Shifter Operation

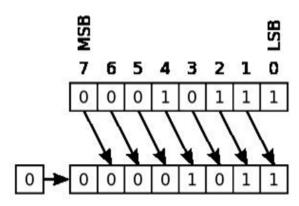

As shown in example below, the LSB bit is removed from the result and the remaining bits are shifter over. The order bits are set to zero.

Figure 4. Example of right shifter

#### II. RIGHT ROTATOR

A right rotator is very similar to a logical right shifter. The differences between the two lies in the manner in which interconnect lines are placed, In particular, since all of the input bits are routed to the output, there is no longer a need for interconnect lines carrying the zero signal. Instead, interconnect lines need to be inserted to enable routing of the low order bits from each row to high order region so that rotate can occur. The longer interconnect lines of the rotator, however, can increase both area and delay.

Figure 5. Right Rotator

#### 2.1 Operation of right rotator:

Rotate is a cyclic shift either to the left or right. This means that as bits are shifted out of the data vector on one side, they are shifted into the data vector on the other side. During this process, all bits from the input are routed to the output. Their position in the output, however,

is not necessarily the same as it was in the input.

An example of rotate right can be seen in the figure 6 where a 8-bit word of data has a one bit rotated right.

Figure 6. Example for right rotator

#### III. RESULTS

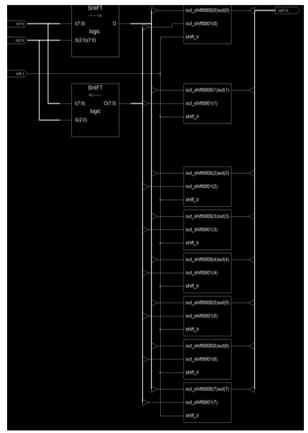

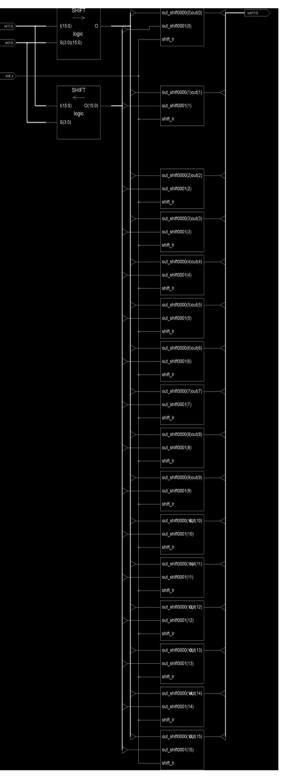

The following figures show the RTL schematics of 8-bit & 16-bit barrel shifter respectively.

Figure 7. RTL schematic of 16-bit barrel shifter

Figure 8. RTL schematic of 16-bit barrel shifter

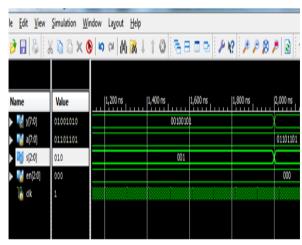

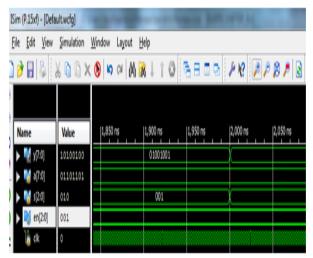

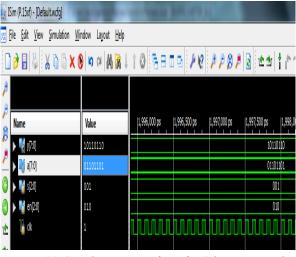

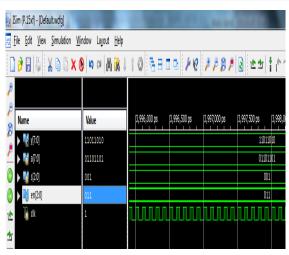

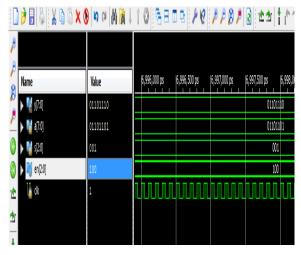

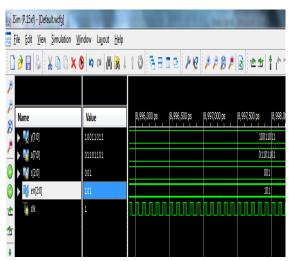

The results shown below are for the 8 bit and 16 bit barrel shifter which shows output waveforms for different operations such as right shift and right rotate.

Figure. 9 Simulation wave form for 8 bit logical left

Figure 10. Simulation wave form for 8 bit logical right shift

Figure 11. Simulation wave form for 8 bit rotate right shift

Figure 12. Simulation wave form for 8 bit rotate left shift

Figure 13. Simulation wave form for 8 bit airthmetic left shift

Figure 14 Simulation wave form for 8 bit airthmetic left right shift

Table 1- Design summary of 8-bit barrel shifter

| Maximum Combinational Path Delay (in ns) for different Barrel Shifter at 8 Bit Level |                                                 |                 |

|--------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|

| O. Anjaneyulu<br>and T. Pradeep<br>and K. Reddy 5                                    | Sajib Kumar<br>Mitra and Ahsan<br>Raj Chowdhury | Result obtained |

| 12.638                                                                               | 22                                              | 8.45            |

Table 2- Design summary of 16-bit barrel shifter

| Maximum Combinational Path Delay (in ns) for different Barrel Shifter at 16 Bit Level |                 |  |

|---------------------------------------------------------------------------------------|-----------------|--|

| Sajib Kumar<br>Mitra and Ahsan Raj<br>Chowdhury [1]                                   | Result obtained |  |

| 40                                                                                    | 15.81           |  |

#### IV. CONCLUSION

We have proposed and designed a Verilog implementation of FPGA based barrel shifter. Which produce appreciable results. It demonstrated that our approach yields & High speed barrel shifter.

#### **REFERENCES:**

- [1] Sajib Kumar Mitra and Ahsan Raja Chowdhury, Optimized Logarithmic Barrel Shifter in Reversible Logic Synthesis, 2015 28th International Conference on VLSI Design and 2015 14th International Conference on Embedded Systems.

- [2] K. Srinivasarao, Gagnesh Kumar, Implementation of Barrel Shifter using Diode free Adiabatic Logic (DFAL), IEEE 2014.

- [3] Md. Shamsujjoha, Hafiz Md. Hasan Babu‡, Lafifa Jamal and Ahsan Raja Chowdhur, Design of a Fault Tolerant Reversible Compact Unidirectional Barrel Shifter, 2013 26th

- International Conference on VLSI Design.

- [4] O. Anjaneyulu, T. Pradeep, C.V. Krishna Reddy, KITS, Design and Implementation of Reversible Logic Based Bidirectional Barrel Shifter, IEEE-ICSE2012 Proc., 2012, Kuala Lumpur, Malaysia.

- [5] Saurabh Kotiyal, Himanshu Thapliyal and Nagarajan Ranganathan, Design of A Ternary Barrel Shifter Using Multiple-Valued Reversible Logic, August 17-20, 2010, IEEE International Conference Korea.

- [6] Daesun Oh and Keshab K. Parhi, Area Efficient Controller Design of Barrel Shifters for Reconfigurable LDPC Decoders, 2008 IEEE.

- [7] Sabyasachi Das and Sunil P. Khatri, A Timing-Driven Approach to Synthesize Fast Barrel Shifters, IEEE Transactions on Circuits and Systems—II: Express Briefs, Vol. 55, No. 1, January 2008

- [8] Sabyasachi Das and Sunil P. Khatri, Timing-Driven Decomposition of a Fast Barrel Shifter, 2007 IEEE.

- [9] S. Palnitkar, "Verilog HDL: A guide to Digital Design and Synthesis", Prentice Hall, Upper Saddle River, NJ, 2003.

- [10] F. Worrell, "Microprocessor Shifter using Rotation and Masking Operations," U.S. Patent 5,729,482, March 1998.

- [11] K. Dang and D. Anderson, "High-Speed Barrel Shifter," U.s. Patent 5,416,731, May 1995.

\* \* \* \* \*