## ASIC Realizations of a Distributed Arithmetic Reconfigurable FIR Filters of Higher Order

#### Rashmi Bawankar

M.Tech Research Scholar ECE Department, NITTTR, Panjab University, Chandigarh (P.B.) [INDIA] Email: rashmi.ece@nitttrchd.ac.in

#### ABSTRACT

Here with this paper, we project an effectual distributed arithmetic (DA) design for execution of digital FIR filter. The projected DA-based design utilizes the sharing method of the look-up table for the computing algorithmic terms i.e. filter outputs as well weight-increment. The quantity of the address is not in direct proportion to the with block size, while the quantity of the flip-flops are not at all dependent on the block size. Which is a crucialadvantage of the projected structure in order to reduce area, when a higher order filter is realized for larger block-sizes. ASIC synthesis result shows that, the anticipated structure for filter of higher orders, has almost 45.62% less area and 3.67% less power dissipation.

**Keywords:**—Distributed Arithmetic Algorithm, Finite impulse response filter, High throughput, Look up table, Optimization.

#### I. INTRODUCTION

Finite impulse response (FIR) digital filters play a vital role in various aspects of the digital signal processing (DSP) [1], [2]. With the time the digital signal processing is becoming prevalent, due to the excellent growth in very large scale integration (VLSI) technology. There is much demand of the he very higher speed FIR filters

#### Rajesh Mehra M.Tech Research Scholar ECE Department, NITTTR, Panjab University, Chandigarh (P.B.) [INDIA] Email:rajeshmehra@nitttrchd.ac.in

realization which consume less power. But as the filter order increases the complexity does increase too and there is the lag in real time operation and computation precision thus decreases, which leads to decrease in the accuracy level of the filter operation. So in order to get a dedicated structural design of the digital FIR filters in ASIC i.e. application specific integrated circuits lots of attempts have, therefore, been made. Distributed Arithmetic algorithm (DA) is a method which is used all over the world so that one can avoid using multipliers to implement sum-of-products computations. It has acquired even more admiration for the large throughput capability as well as regularity which has further resulted into area-time efficient and the cost-effective for computation [1].

DA is frequently used to form efficiently Multiply-Accumulate Computation the circuit (MAC) for various FIR filters and various Digital Signal Processing (DSP) applications. The high computational efficiency is the key benefit of DA [2]. The conservative multipliers are not required as multiplication DA allocates and accumulation operations through shifters, lookup-tables (LUT), and the adders. The DA code generation supports for the fixedpoint filters designs only [3]. So distributed arithmetic can also be used for the higher

233

order filters. In order to improvise throughput, the simple DA algorithm is modified and it computes additional one bitwise sum at a time. The amount of instantaneously calculated bit wise sums is stated as twos power а termed The the Distributed Arithmetic radix. multipliers in MAC unit of many DSP functions have more power and area requirements. The LUT in Distributed arithmetic utilizes more memory. [7].

#### II. FIR FILTER DESIGN BASED ON DA

At an instant n, the outcome y[n] of an Ntap FIR digital filter with recent ingoing sample x[n] is given such as

$$y[n] = \sum_{i=0}^{N-1} w[i]x[n-i]$$

(1)

Where, w[i] (i = 0, 1, 2, 3, 4,..., N - 1) signifies filter weights. Through signifying each and everyingoing samples i.e. x[n - i]in two's complement, we get

$$\mathbf{x}[\mathbf{n}-\mathbf{i}] = \mathbf{x}_{\mathbf{n}-\mathbf{i}} = -\mathbf{b}_{\mathbf{i},\mathbf{B}+1} + \sum_{j=1}^{\mathbf{B}-1} \mathbf{b}_{\mathbf{i},\mathbf{B}-1-j^{2-j}}$$

(2)

By substituting (2) into (1) and rearranging, we get

$$y[n] = \sum_{j=0}^{B-1} c_{B-1-j^{2-j}}$$

(3)

where  $c_{B-1-j} = \sum_{i=0}^{N-1} w_i b_{i,B-1}$ (j≠0)

$$\mathbf{c}_{\mathsf{B}-1} = -\sum_{i=0}^{\mathsf{w}} \mathbf{w}_i \mathbf{b}_{i,\mathsf{B}-1}$$

For a given set of w[i] (i = 0,1,2,3,4, .....N - 1), the terms cB-1-j would consider only one combination out of 2N probable combinations, which can be calculated well before and stacked in a look table. The Distributed Arithmetic up execution of a 4-tap Finite Impulse Response filter is represented in Fig. 1. At some extent the arriving bits of the input is stacked in particular order such as, the latest input samples are stacked in the topmost register whereas an old input sample is stacked in the bottom most register. The address line for the LUT is formed by the LSB of the registers which the partial product term. contains Afterwards these partial product terms are shifted and then accumulated for the "b" number of the clock cycles, which then produces the single sample output.

Figure 1. Block diagram of the digital Filter using multipliers.

#### **III. PROPOSED DA BASED FILTER**

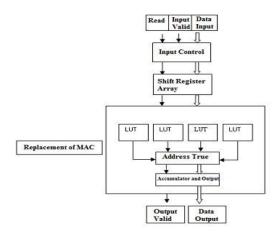

The anticipated configuration of the Distributed Arithmetic constituted FIR digital filter meant for ASIC application is as represented in Fig. 2. Input tasters  $\{x(n)\}$ coming on each sampling time are provided to a (SIPOSR) serial-in-parallel-out shift register having size N. The serial-inparallel-out shift register (SIPOSR) crumbles N latest utmost samples towards P vectors bp of the length M for p = 0,1,2,3,4,  $\dots, P - 1$  and provides these towards P reconfigurable partial product generators to analyze the partial products conferring to [19, 20]. For better-throughput execution, reconfigurable partial the product

generators(RPPG) creates L partial products conforming to L bit slices in parallel by utilizing the look up table poised of a very single register bank of 2M - 1 registers and L number of 2M : 1 MUXes [21].

Figure 2. Bock Diagram of Implementation of FIR filter using DA

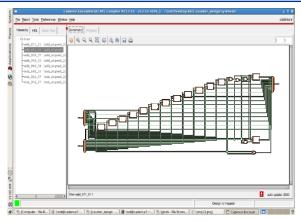

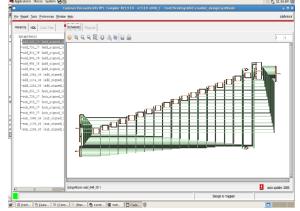

In the projected assembly, the reduced storing ingestion by means of involving each and every look up table across L bit slices is given. The register array is being chosen for this very perseverance rather than memory-based look up table, so that to access the Look Up Table contents at once. Along with, the fillings in register-based Look Up Table is able to get update in parallel in lesser cycles compared to the memory-based look up table to execute anticipated FIR filter [22, 23]. Width of each and every register with the look up table is  $(W + \lceil \log_2 M \rceil)$  bits, whereas W is the word-length of filter coefficient. The input of the MUXes are 0, h(2p), h(2p + 1), and h(2p) + h(2p + 1); and the two-bit digit bl, p is fed to MUX l for  $0 \le l \le L - 1$  as a control word. We can find that MUX 1 provides the partial product SI, p for  $0 \le l \le$ L - 1 given by [20]. In the figure 3 and figure 4 the higher order filters i.e. 64 and 128 of the proposed FIR filter design based on the distributed arithmetic is shown respectively.

Figure 3. Proposed structure for 64-order FIR filter based on DA scheme

Figure 4. Proposed structure for 128-order FIR filter based on DA scheme

#### **IV. RESULTS AND DISCUSSIONS**

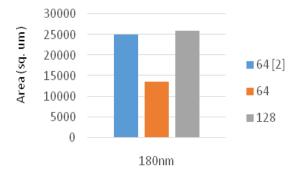

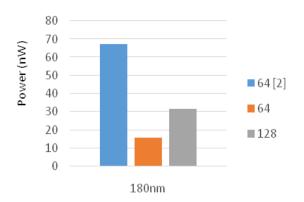

The execution of FIR filter for ASIC implementation has been observed and validated, which refers that proposed fir filter structure compared to that of the DA based structure in [2], results are to be taken in terms of area utilized, the power dissipated as well as speed performance for 64bits and 128bits filter order. The anticipated assembly has smaller area as well as lesser power consumption quated with that of the Distributed Arithmeticbased structure [2].In fig.5 shows the results of the projected method as well as the earlier method by utilizing a 180-nm standard cell library. The anticipated structure uses less area on the chip level which shows that combinational logic is less used and thus reduce computation

235

complexity. As the logic blocks are reduced the power consumption is less and even the speed has been increased compared to that of the existing work.

| Pa-<br>rameter<br>s | [2]   | Proposed | Proposed | Percentage<br>Improve-<br>ment |

|---------------------|-------|----------|----------|--------------------------------|

| Filter<br>Length    | 64    | 64       | 128      | %                              |

| Area<br>(sq.um)     | 24939 | 13563    | 25981    | 45.62                          |

| Power<br>(nW)       | 67.23 | 15.71    | 31.73    | 3.27                           |

| Speed (ns)          | 6.81  | 1.1995   | 1.1992   | 4.67                           |

# Table 1: Performance Comparison ForL=M=64

Figure 5. Area Comparison for 90 and 180nm technology.

Figure 6. Power Comparison for 90 and 180nm technology

V. Conclusion

In this brief, an effectual structure aimed at order digital higher FIR filter for reconfigurable Distributed Arithmetic based ASIC application is presented. It has predicted that the structure hardware cost possibly will be determined by partaking the similar registers by means of the Distributed Arithmetic units meant for various bit slices. The projected plan has almost less area along with power consumption for the ASIC implementation. The design will able to be adopted to higher order filters. The percentage improvement speed is 4 times, while in power consumption is 3 times less and even area is decreased by 45%.

### **REFERENCES:**

- [1] S. Y. Park, P. K. Meher, "Efficient FPGA and ASIC Realizations of a DA -Based Reconfigurable FIR Digital Filter", IEEE Transactions on Circuits and Systems-II, Express Briefs, Vol. 61, No. 7, pp. 511-515, July 2014.

- [2] M. Surya Prakash, R. A. Shaik," Low-Area and High-Throughput Architecture for an Adaptive Filter Using Distributed Arithmetic," IEEE Transactions on Circuits and Systems-II, Express Briefs, Vol. 60, No. 11, pp. 781-785, November 2013.

- [3] S. Y. Park, P. K. Meher, "Low Power, High-throughput, and Low Area FIR Filter Adaptive Based on Distributed Arithmetic", IEEE Transaction on Circuits and Systems-II, Express Briefs, Vol. 60, No. 6, pp. 346-350, June 2013.

- [4] B. K. Mohanty, P. K. Meher, "A High -Performance Energy-Efficient Architecture for FIR Adaptive Filter Based on New Distributed Arithmetic Formulation of Block LMS

Algorithm," IEEE Transactions on Signal Processing, Vol. 61, No. 4, pp. 921-932, February 2013.

- R. Guo and L. S. DeBrunner. "Two [5] High-Performance Adaptive Filter Implementation Schemes using Arithmetic," Distributed IEEE Circuits Transaction System II. Express Briefs, Vol. 58, No. 9, pp. 600-604, September 2011.

- [6] S. Baghel and R. Shaik, "FPGA Implementation of Fast Block LMS Adaptive Filter using Distributed Arithmetic for High-Throughput," IEEE International Conference Communication Signal Processing (ICCSP), pp. 443–447, February 2011.

- [7] P. K. Meher, S. Chandrasekaran, and A. Amira, "FPGA Realization of FIR Filters by Efficient and Flexible Systolization using Distributed Arithmetic," IEEE Transaction Signal Processing, Vol. 56, No. 7, pp. 3009– 3017, July 2008.

- [8] S. Baghel and R. Shaik, "Low Power and Less Complex Implementation of Fast Block LMS Adaptive Filter using Distributed Arithmetic," IEEE Students Technology Symposium, pp. 214–219, January 2011.

- [9] D. J. Allred, H. Yoo, V. Krishnan, W. Huang and D. V. Anderson, "LMS Adaptive Filters using Distributed Arithmetic for High Throughput," IEEE Transaction Circuits System, Vol. 52, No. 7, pp. 1327–1337, July 2005.

- [10] M. S. Prakash and R. A. Shaik, "DA Based Approach for the Implementation of Block Adaptive Decision Feedback Equalizer," IET

Signal Processing, Vol.10, No.6, pp. 676-684, August 2016.

- [11] A. Nanda, T. Vigneshwaran and Ashwani K. Rana, "DA-Based Efficient Testable FIR Filter Implementation on FPGA Using Reversible Logic," Springer- Circuit, Systems, and Signal Processing, Vol. 33, No. 3, pp. 863-884, March 2014.

- [12] P. K. Meher and S. Y. Park, "Highthroughput pipelined realization of adaptive FIR filter based on distributed arithmetic," IEEE/IFIP, 19th International Conference VLSI-SOC, pp. 428–433, October 2011.

- [13] R. Guo and L. S. DeBrunner, "A Novel Adaptive Filter Implementation Scheme using Distributed Arithmetic," Forty Fifth Asilomar Conference on Signals, System, Computers, pp. 160–164, November 2011.

- [14] D. J. Allred, H. Yoo, V. Krishnan, W. Huang, and D. V. Anderson, "A Novel High Performance Distributed Arithmetic Adaptive Filter Implementation on an FPGA," IEEE International Conference Acoustic, Speech, Signal Processing (ICASSP), Vol. 5, pp. 161-164, 2004.

- S. A. White, "Applications of Distributed Arithmetic to Digital Signal Processing: A tutorial review," IEEE Magazine, Vol. 6, No. 3, pp. 4– 19, July 1989.

- [16] T. Hentschel, M. Henker, and G. Fettweis, "The Digital Front-end of Software Radio Terminals," IEEE Personal Communication Magazine Vol. 6, No. 4, pp. 40–46, August 1999.

237

- [17] L. Ming and Y. Chao, "The Multiplexed Structure of Multichannel FIR Filter and Its Resources Evaluation," International Conference on Computer Distributed Control and Intelligent Environment Monitoring, pp. 764–768, March 2012.

- [18] I. Hatai, I. Chakrabarti, and S. Banerjee, "Reconfigurable Architecture of а RRC FIR Interpolator for Multi-standard Digital Up Converter," IEEE 27th International Symposium on Parallel & Distributed Processing, Workshops and PhD Forum, pp. 247–251, May 2013.

- [19] P. K. Meher, "Hardware-efficient Systolization of DA-based Calculation of Finite Digital Convolution," IEEE Transaction Circuits System II, Express Briefs, Vol. 53, No. 8, pp. 707–711, August 2006.

- [20] E. Ozalevli, W. Huang, P. E. Hasler, and D. V. Anderson, "A Reconfigurable Mixed-signal VLSI Implementation of Distributed Arithmetic used for Finite-impulse Response Filtering," IEEE Transaction Circuits System I, Registered Papers, Vol. 55, No. 2, pp. 510–521, March 2008.

- [21] Rajesh Mehra, Lajwanti Singh, "FPGA based Speed Efficient Decimator using Distributed Arithmetic Algorithm," International Journal of Computer Applications, Vol. 80, No. 11, pp. 37-40, October 2013.

- [22] Rajesh Mehra, Swapna Devi, "FPGA Based Design of High Performance Decimator using DALUT Algorithm," ACEEE International Journal on Signal and Image Processing, Vol. 1, No. 2, pp. 9-13, July 2010.

- [23] K. H. Chen and T.-D. Chiueh, "A L o w - p o w er D i g i t - b a s e d Reconfigurable FIR Filter," IEEE Transaction Circuits System II, Express Briefs, Vol. 53, No. 8, pp. 617–621, August 2006.

- [24] P. V. Rao and Jhansi Bai, "Efficient FPGA and ASIC Realization of a DAbased Reconfigurable FIR Digital Filter", International Journal of Professional Engineering Studies, Vol. 5, No. 4, pp. 257-263, August 2015.

- [25] Rajesh Mehra, Ravinder Kaur, "FPGA based Efficient Interpolator design using DALUT Algorithm," Conference Presentation on Spartan Random Field, pp.51-62, January 2011.

\* \* \* \* \*