# An Efficient Technique for Implementing Low Power Fir Filter

## Gonrathi Naresh

Assistant Professor, Department of Electronics and Communication Engineering, Scient Institute of Technology, Jawaharlal Nehru Technological University Hyderabad (T.S.), [INDIA] Email: gonrathinaresh@gmail.com

#### ABSTRACT

Memory based structures are utilized in numerous sort of digital signal processing (DSP) application. Memory-based structures are better execution In territory minimization contrast and increase aggregate structures and have numerous different focal points like diminished inertness since the memory-get to time is a lot shorter than the standard duplication time contrasted with the regular multipliers. The multiplier utilizes LUT's as memory for their calculations. The antisymmetric product coding (APC) and oddvarious capacity (OMS) methods were utilized for look up table (LUT) in versatile FIR Memory-based structure, for channel. example, APC and OMS systems are utilized for proficient Multiplication. Thus, the mix of these two strategies gives decrease in LUT size to one fourth in versatile FIR channel when contrasted and the traditional Look up Table (LUT) of versatile FIR filter.

*Keywords* :— Look-up-Table (LUT),Digital Signal Processing, Odd Multiple Storage (OMS)

### I. INTRODUCTION

The efficient implementation of digital signal processing algorithms has always been critical for the design of embedded systems suitable for real time applications.

The power-performance trade-off is being encountered in the design of Finite Impulse Response (FIR) digital filters, which are the fundamental components of several DSP algorithms for DSP core realization Although their general architecture permits an easy implementation, it requires an excessive amount of hardware complexity, leading also to significant amount of power. Thus, many design techniques have been presented by the researchers targeting the reduction of total power dissipation. The VLSI manufacturing technologies states that the dynamic power dissipation has been found to be the dominating factor of total power consumed, compared to the leakage current. In a CMOS VLSI implementation, dynamic power dissipation is strongly dependent on the switching activity of inputs and outputs of the circuit. Hence several design techniques have to be explored for the design and implementation of high throughput FIR filters with low complexity and reduced switching activity per output sample.

### II. FIR FILTER DESIGN USING COEFFICIENT REUSABILITY TECHNIQUE

At the point when explicit DSP compositional decisions were made the focal point of multiplier design and number portrayal must be cautiously considered.

182

The impact of DSP architectural realization, multiplier type, and the choice of number representation on the overall power consumption of DSP devices. Digital FIR channels are utilized in sign preparing like commotion crossing out and channel evening out. The FIR channel yield as depicted in condition is acknowledged by a huge number of adders, multipliers and defer components. The equipment and power can be enhanced by constrained architectural transformations.

$$Y[n] = \sum_{k=0}^{N-1} h[k] * X[n-k]$$

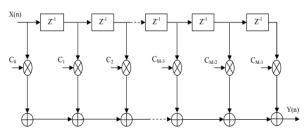

where Y[n] is the filter output, X[n-k] is input data and h[k] is the filter coefficient. Figure 1 shows a Direct Form (DF) implementation of the FIR filter

Figure 1: Direct Implementation of FIR filter.

A DF channel actualized on a solitary multiplier DSP has been executed with the end goal that at each clock another example x(n) and the relating channel coefficient h (k) are brought from the memory at the same time and connected to the multiplier. In this manner, for every augmentation the two contributions of the multiplier get new information. Because of this consistent change at the two data sources, the utilization of DF acknowledgment is relied upon to cause abnormal state of exchanging movement at both multiplier inputs. This a comparing high will thus cause exchanging action inside the multiplier, prompting higher generally speaking force utilization. In any case, the exchanging movement at information contributions of

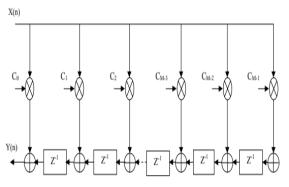

the multiplier is significantly reduced using the Transposed Direct form (TDF) realization since the data input remains unchanged for a substantial number of multiplication operations. This results in considerable reduction in switching activities within the multiplier circuit and consequently leads to less power consumption than DF realization. An equivalent architecture in the TDF is shown in Figure 2.

Figure 2: Transposed direct form implementation of FIR filter.

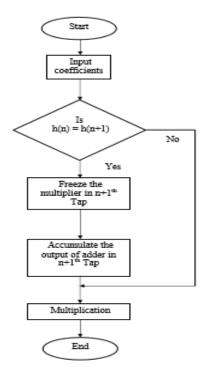

From the transposed architecture obviously the multiplier plays a significant job in FIR channel and the quantity of multiplication and addition task relies on the quantity of taps utilized. The general power utilization of the FIR channel is decreased by limiting the power utilization of the snake and multiplier. The power utilization of the FIR channel can be diminished utilizing the created crossover encoded multiplier to duplicate the information esteem x(n) and coefficient h(n). The method disables the capacity of multiplier when the sequential channel coefficient esteems are same. By this technique both the switching activity and power consumption of the FIR filter are reduced. Figure 3 provides the flow chart of developed coefficient reusability the technique. By this procedure both the exchanging action and power utilization of the FIR channel are decreased. Figure 3 gives the stream outline of the created coefficient reusability method.

183

*Figure 3: Flow graph of Coefficient reliability technique implementation.*

# 2.1 Structure of Coefficient Reusablity Technique

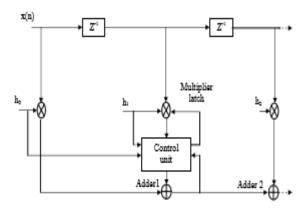

The structure of developed reusability technique is shown in Figure 4.

Figure 4 Structure of Coefficient reusability technique

The control unit checks the similarity, in the event that h0 and h1 are same, at that point the control unit locks the multiplier in Tap1. The yield of Adder1 is aggregated and the activity of the multiplier is evaded which makes the exchanging action and power utilization diminished.

### **III. ALGORITHM**

DA is an important FPGA technology. To understand the DA design paradigm consider the "sum of products" inner product shown below

$$y = \sum_{n=0}^{N-1} A_n * x_n \tag{1}$$

$A_n$  is known as constants and  $x_n$  is a variable. An unsigned DA system assumes that the  $x_n$  is represented by

$$x_n = \sum_{b=0}^{\beta-1} 2^b x_{n,b} \quad \text{with} \quad x_{n,b} \in [0,1]$$

(2)

Where  $x_n$ , b denotes the b<sup>th</sup> bit of  $x_n$  the nth sample of x. The inner product can, therefore be represented as

$$y = \sum_{b=0}^{\beta-1} 2^{b} \sum_{n=0}^{N-1} A_{n} x_{n,b}$$

(3)

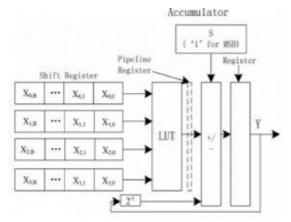

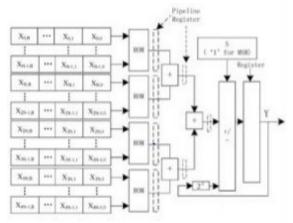

Figure 5: FIR filters implementation with single LUT.

### **IV. LUT LESS FIR IMPLEMENTATION**

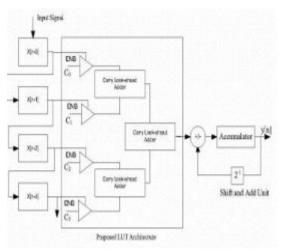

The architecture proposed in this paper is appeared in Figure 7. In this architecture, the tristate buffer and a convey look-ahead the fundamental viper are advanced rationale units used to develop the on-line LUT. From this engineering plainly channel coefficients will go to the CLA just if their support empower sign esteem is 1.A table (LUT)customary query based multiplier, where A will be a fixed coefficient and X is an info word to be duplicated with A. Accepting X to be a positive double number of word length L, there can be 2L potential estimations of X and in like manner, there can be 2L potential estimations of item

C = A X. Therefore, for memorybased duplication, a LUT of 2L words, comprising of pre processed item esteems comparing to every conceivable estimation of X, is expectedly utilized.

Figure 7 : LUT less FIR Implementation

### **IV. CONCLUSION**

DA architecture and performance analyzing presents a new architecture for DALUT. The proposed architecture uses the main concept of basic DA technique by implementing MAC unit. The results obtained shows the computation time and the area used is reduced. The proposed architecture in our paper can be easily used to implement high order FIR filters.

### **REFERENCES:**

- Antonion, A., 1993. Digital Filters: Analysis, Design and Applications, McGraw-Hill, New York. Kung, H.T., 1982. Why systolic architecture? IEEE Computer 15(1): 37-45.

- [2] Yu, S. and E.E. Swartzlander, 2001. DCT implementation with distributed arithmetic, IEEE Transactions on Computers, 50(9): 985-991.

- [3] Hanho Lee and Gerald E. Sobelman, 2002. FPGA-based digit-serial CSD FIR filter for image signal format conversion, Microelectronics Journal, 33(5-6): 501-508.

- [4] Valeria Garofalo, 2008. Fixed-width multipliers for the implementation of efficient digital FIR filters, Microelectronics Journal, 39(12): 1491-1498.

- [5] Lei Zhang and Tadeusz Kwasniewski, 2009. FIR filter optimization using bit -edge equalization in high-speed backplane data transmission, Microelectronics Journal, 40(10): 1449-1457.

- [6] Eshtawie, M.A.M. and M. Othman, 2006. On-line DA-LUT architecture for high-speed high-order digital FIR filters, in: Proceedings of the IEEE International Conference on Communication Systems (ICCS), Singapore, November.

- [7] Choi, J.P., S.C. Shin and J.G. Chung, 2000. Efficient ROM size reduction for distributed arithmetic, in: Proceedings of the IEEE International Symposium Circuits Systems (ISCAS), May 2000, pp: 61-64.

- [8] Sanjay, Attri, B.S., Sohi and Y.C. Chopra, 2001. Efficient design of application specific DSP cores using FPGAs, in: International Conference on ASIC Proceedings, pp: 462-466.

- [9] Kim Kyung-Saeng and Kwyro Lee, 2003. Low-power and area efficient FIR filter implementation suitable for multiple tape, IEEE Transactions on VLSI Systems, 11(1) (February 2003).

\* \* \* \* \*